# 外部碎裂記憶體控制單元 之電路設計

指導教授:陳仁德教授

專題成員:黃楷雋 吳思蓓 官學勤 傅紹齊

## 專題內容

| 時間            | <b>內容</b>                  |

|---------------|----------------------------|

| 108.5 ~ 109.3 | IC設計競賽考古題演練(1999年~2019年試題) |

| 109.3.25      | 參加108學年教育部大學校院IC競賽         |

| 109.4 ~ 109.6 | 電路設計實例製作                   |

#### 競賽考古題

## 參賽題目(組別,上傳時間)

## 電路設計實例製作(+題目從哪裡來)

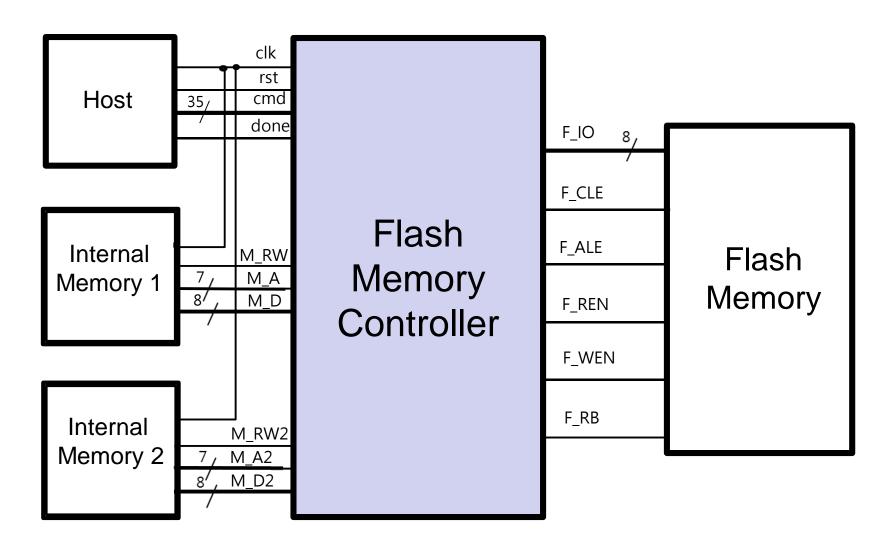

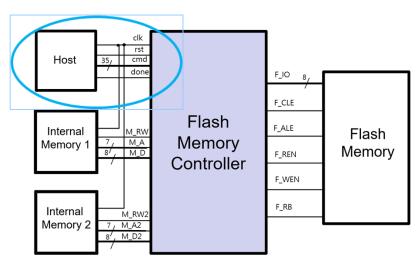

實作快閃記憶體控制單元在內部記憶體及快閃記憶體之間的寫入及讀取,並用以解決記憶體外部碎裂之問題,設計電路並合成。

#### 系統方塊圖

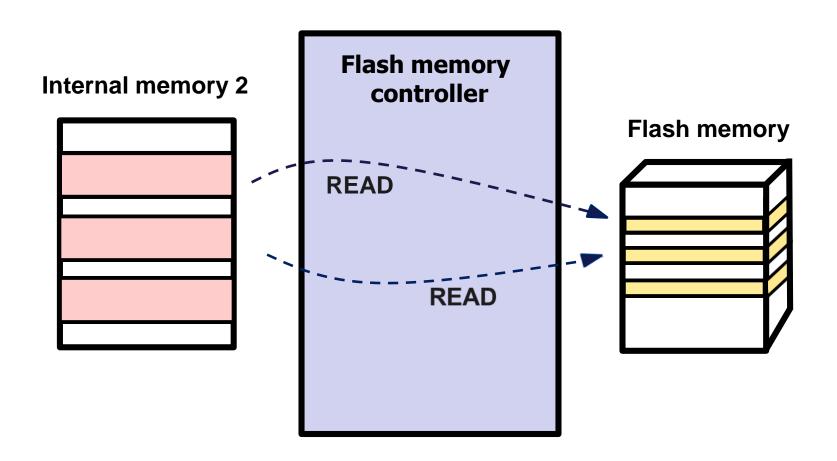

## 讀取多筆不連續資料

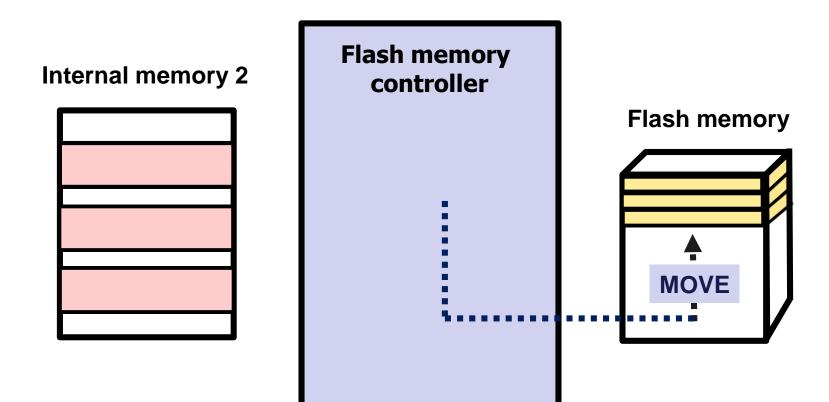

#### 解決外部碎裂

## 主控端輸出入信號表

| 信號名稱 | 輸出/輸入  | 位元寬度 | 說明                                                                                     |

|------|--------|------|----------------------------------------------------------------------------------------|

| clk  | Input  | 1    | 時脈信號<br>主控端與內部記憶體於時脈正缘時動作                                                              |

| rst  | Input  | 1    | 高位準非同步之系統重置信號<br>此信號於系統啟動時送出                                                           |

| cmd  | Input  | 35   | 指令輸入信號<br>本控制器需根據此指令來對快閃記憶體<br>進行讀寫等動作                                                 |

| done | output | 1    | 完成指令輸出信號<br>當此信號為low時表示控制電路正在對<br>快閃記憶體進行讀寫,此信號為high時<br>表示控制電路完成讀寫指令,主控端也會<br>發出下一筆指令 |

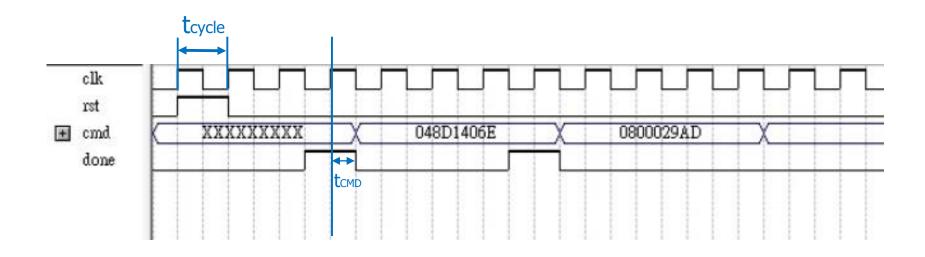

#### 主控端系統時序

## 內部記憶體輸出入信號表

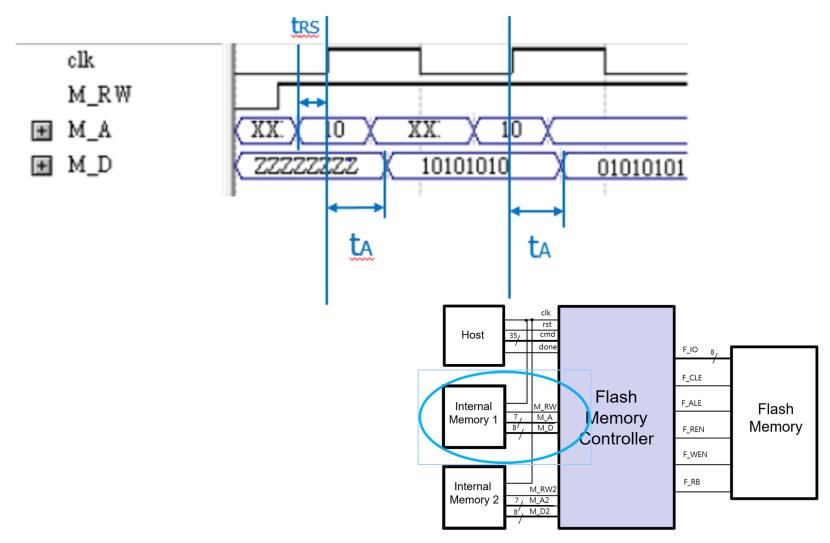

| 信號名稱            | 輸出/輸入  | 位元寬度 | 說明                                                           |

|-----------------|--------|------|--------------------------------------------------------------|

| M_RW /<br>M_RW2 | Output | 1    | 內部記憶體讀寫控制信號<br>當此信號為high時是對內部<br>記憶體進行讀取;low則是進行<br>對內部記憶體寫入 |

| M_A / M_A2      | Output | 7    | 內部記憶體七位元位址                                                   |

| M_D / M_D2      | inout  | 8    | 內部記憶體八位元雙向資料輸<br>出入埠                                         |

#### 內部記憶體系統時序

## 快閃記憶體輸出入信號表

| 信號名稱  | 輸出/輸入  | 位元寬度 | 說明                                                                                                                      |

|-------|--------|------|-------------------------------------------------------------------------------------------------------------------------|

| F_IO  | Inout  | 8    | 快閃記憶體八位元雙向輸入出埠<br>此輸出入埠可被視為輸入指令,輸入位址<br>及輸出資料                                                                           |

| F_CLE | Output | 1    | 快閃記憶體指令致能信號<br>當此信號為high時, F_IO會被視為 <mark>指令</mark> ,<br>且快閃記憶體於F_WEN為正緣讀取指令                                            |

| F_ALE | Output | 1    | 快閃記憶體位址致能信號<br>當此信號為high時, F_IO會被視為 <mark>位址</mark><br>且快閃記憶體於F_WEN為正緣讀取位址                                              |

| F_REN | Output | 1    | 快閃記憶體連續讀取致能信號<br>在進行資料的連續讀取時,資料會在此信<br>號 <mark>負緣後經過tREA</mark> 的時間出現於F_IO,同<br>時將快閃記憶體內的位址加1.若F_IO為<br>輸出時,此信號須維持在high |

## 輸出入信號表

| 信號名稱  | 輸出/輸入  | 位元寬度 | 說明                                                                                |

|-------|--------|------|-----------------------------------------------------------------------------------|

| F_WEN | Output | 1    | 快閃記憶體寫入致能信號<br>當F_IO為指令,位址及資料輸入時,由此信<br>號的正緣來對快閃記憶體進行寫入.<br>若F_IO為輸入時,此信號須維持在high |

| F_RB  | input  | 1    | 快閃記憶體完成/忙碌信號<br>當此信號為low表示快閃記憶體正在忙碌,<br>要等待此信號為high才能進行動作<br>(重置指令除外)             |

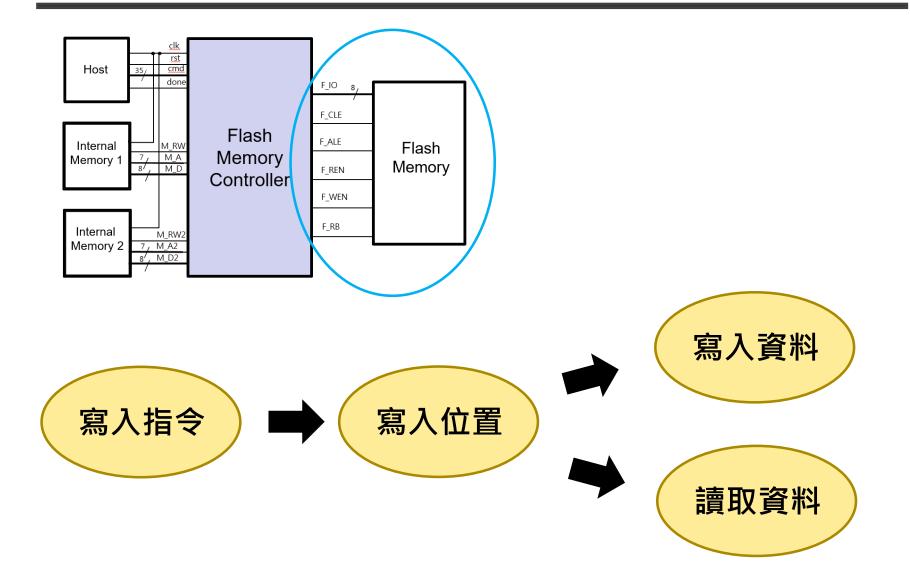

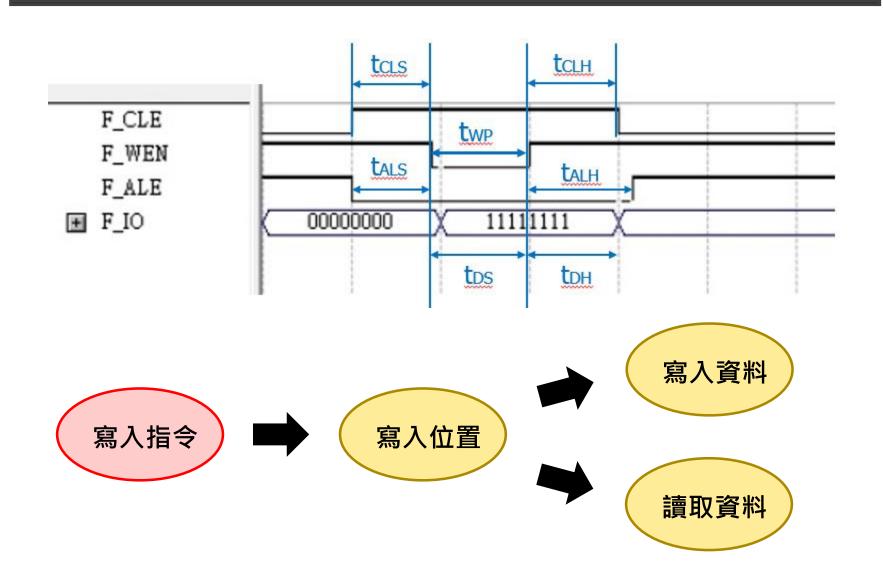

#### 快閃記憶體

## 快閃記憶體指令週期

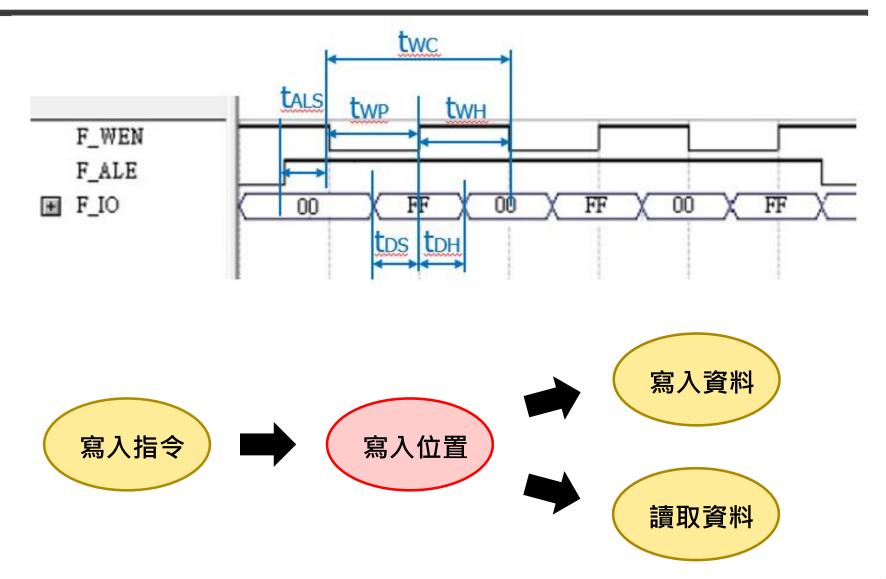

#### 快閃記憶體位置週期

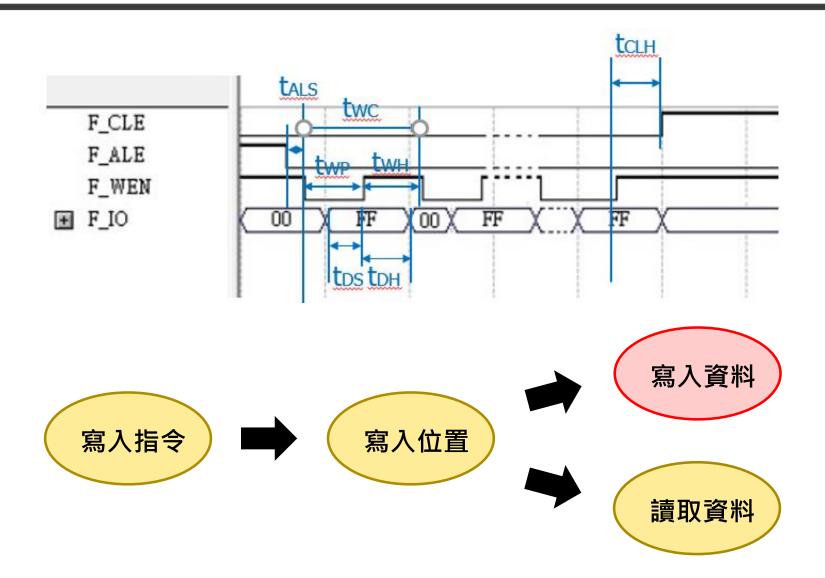

#### 快閃記憶體資料輸入

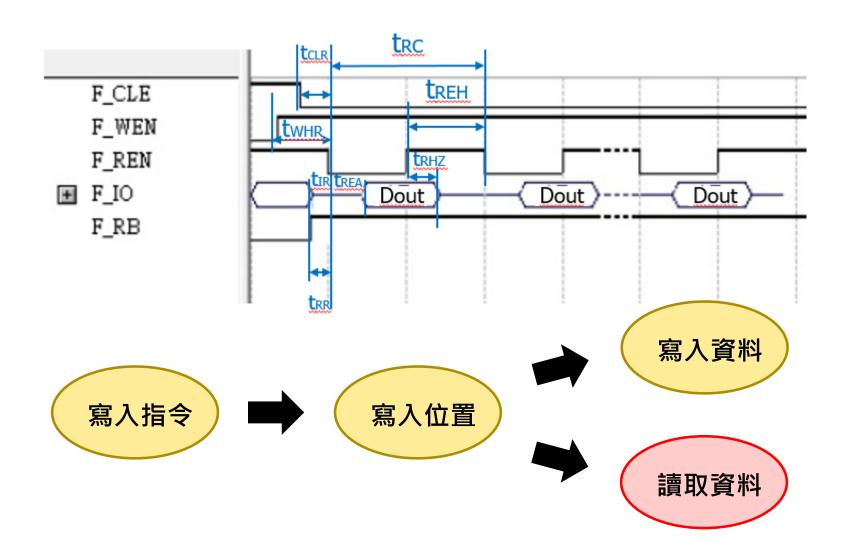

#### 快閃記憶體資料讀取

## 指令格式

#### **Write Opetation**

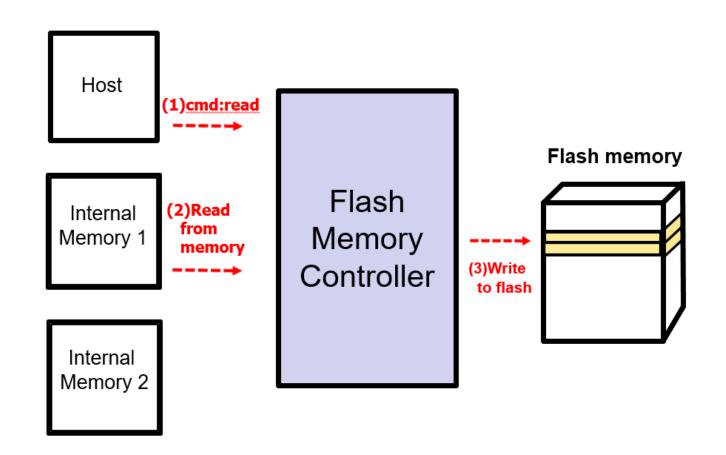

cmd 000:write,讀取內部記憶體資料,並將資料寫入快 閃記憶體內。

#### **Read Operation**

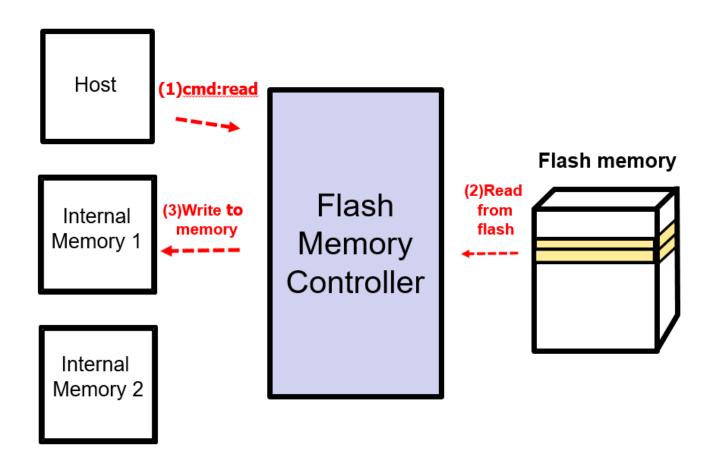

cmd 001: read,將資料由快閃記憶體讀取,並將這些資料寫入內部記憶體。

#### **Compact Operation**

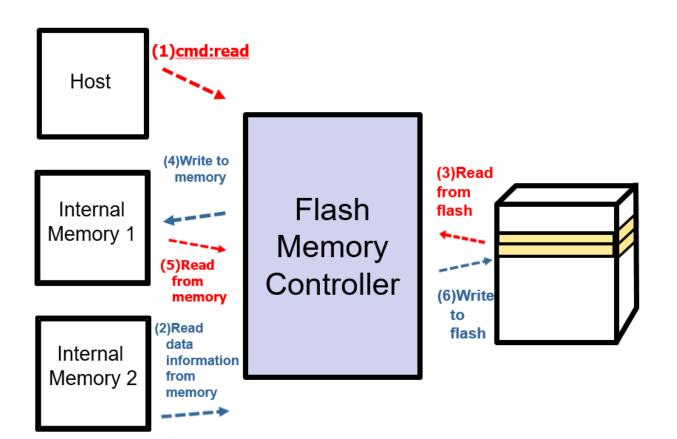

cmd 010: compaction,於內部記憶體2讀入資料相關資訊(起始位置及長度),藉由這些資訊,上推快閃記憶體內容,解決外部碎裂問題。

## 實驗結果(+語言, 改大寫

Logic Simulator : modelsim 18.0

Logic Synthesizer : Design Compiler v2008.09-sp2

Process File : CBDK\_TSMC90GUTM\_Arm\_f1.0

Language : Verilog

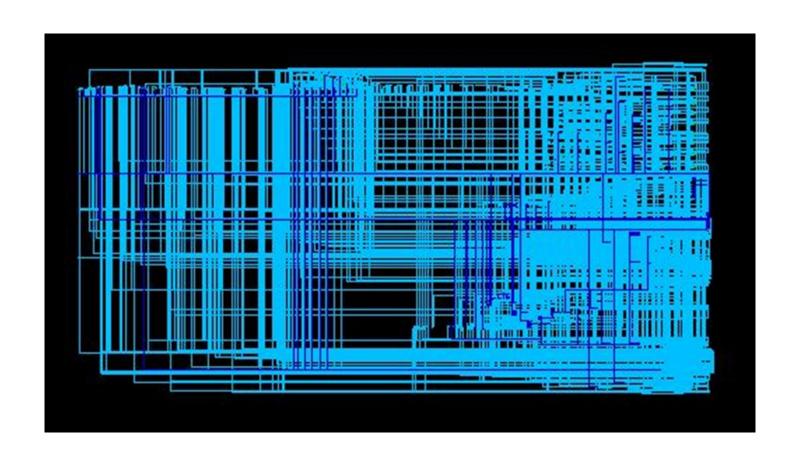

#### 電路圖

#### Area

```

Cell Count

Hierarchical Cell Count:

Hierarchical Port Count: 130

Leaf Cell Count:

1728

Buf/Inv Cell Count:

742

CT Buf/Inv Cell Count:

Area

Combinational Area: 6831.619288

Noncombinational Area: 2632.593657

Net Area:

0.000000

Cell Area:

9464.212945

Design Area:

9464.212945

```

## 結論(改多點段落)

以IC競賽題目做延伸,更改其內部記憶體的數量與測資, 實作外部碎裂之處理,使非連續資料得以聚集在一起,形 成夠大的連續可用區塊。並探討其晶片大小與速度。

## 參考文獻(加中文,改恐龍本)

http://icdc.ee.nsysu.edu.tw/history/CellBasedDesign/200 9\_A\_univ/2009\_A\_univ.rar

https://en.wikipedia.org/wiki/Fragmentation\_(computing)